What are the principles of PCB decoupling capacitor configuration?

In DC power supply circuit, the change of load will cause power supply noise. For example, in a digital circuit, when the circuit changes from one state to another, a large spike current will be generated on the power line, forming a transient noise voltage. Decoupling capacitors can suppress the noise caused by load changes, which is a common practice in reliability design of printed circuit boards. So, what are the principles for configuring decoupling capacitors on PCB?

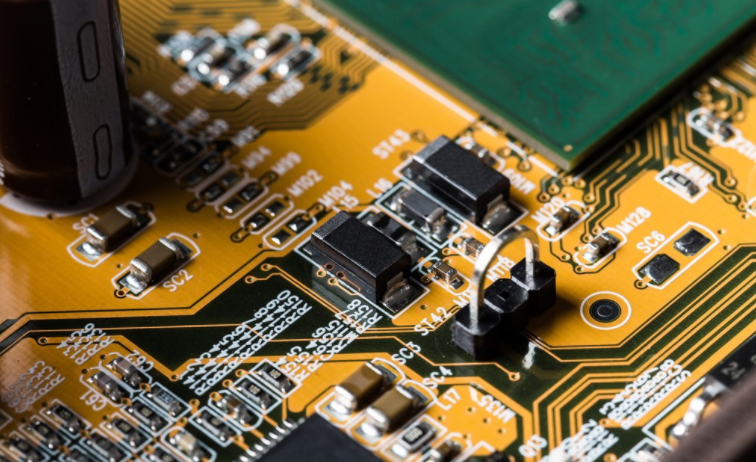

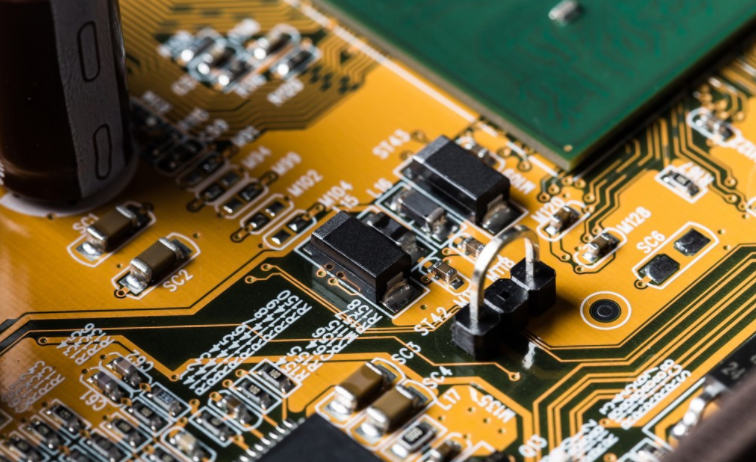

PCB PCB decoupling capacitor configuration

1. The power input terminal is connected with an electrolytic capacitor of 10~100uF. If the position of the printed circuit board allows, the anti-interference effect of the electrolytic capacitor of more than 100uF will be better.

2. Each IC chip is equipped with a 0.01uF ceramic capacitor. If the space of the printed circuit board is too small to fit, a 1~10uF tantalum electrolytic capacitor can be configured for every 4~10 chips. The high-frequency impedance of this device is very small. The impedance is less than 1 Ω in the range of 500kHz~20MHz, and the leakage current is very small (less than 0.5uA).

3. For devices with weak noise capacity and large current change during shutdown and memory devices such as ROM and RAM, decoupling capacitors should be directly connected between the power line (Vcc) and ground wire (GND) of the chip.

4. The lead of decoupling capacitor shall not be too long, especially the high frequency bypass capacitor shall not have lead.

The above is the explanation given by the editor of pcb circuit board company. If you want to know more about PCBA, you can go to our company's home page to learn about it. In addition, our company also sells various circuit boards,

High Frequency Circuit Board and SMT chip are waiting for your presence again.