Issues that occur at the chip, package, and printed circuit board levels during IP integration interact in all three domains in the form of signal integrity (SI) and power integrity (PI) issues. Signal integrity issues include timing effects (resulting from edge-rate impaired jitter that worsens with rising frequency) and amplitude effects such as electromagnetic interference (EMI), including low and high frequency crosspoilers and harmonics. Power integrity issues include switching noise and crosstalk, which must be managed dynamically so as not to affect function and performance.

This is a challenging situation due to the need to maintain clean power levels and noise tolerances as the V dd descends synchronously with deeper submicron nodes. One cannot fail to notice the many commonalities between these problems and the methods used to reduce them at all three levels of system design and integration. After realizing that IP integration problems were caused by a design approach that did not treat chip, packer, and PCB design as an integrated whole, efforts were made to develop an approach that could successfully deal with this multivariate confusion. From this came the concept of distribution network or PDN.

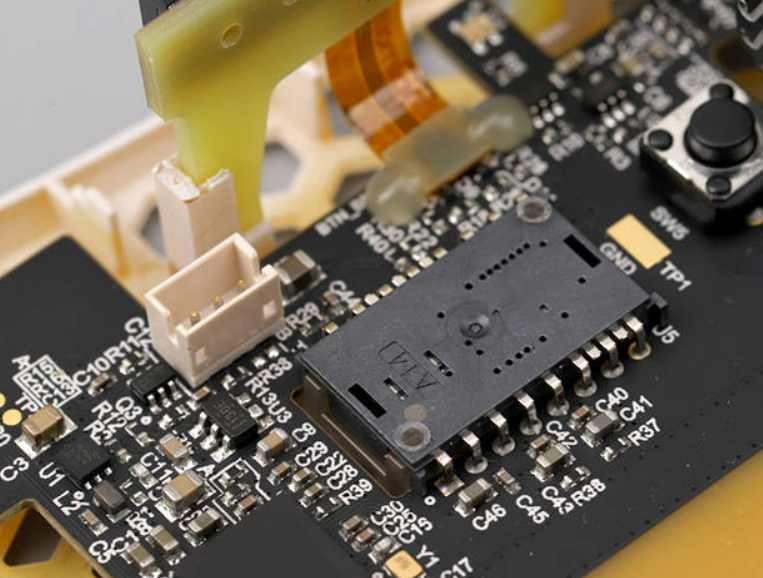

The grounding layer in the package and PCB blocks crosstalk from the signal layer and blocks noise from EMI. However, both levels risk frequency-dependent resonance between the ground layer and the power layer, almost certainly requiring decoupling. Silicon through-hole (TSV) and die through-hole (TMV) in packaging have emerged as potential sources of crosstalk at all three levels. This problem can be mitigated by proper spacing, scattered ground overholes between signal overholes, differential signals, and the shortest distance to ground reference. This fix is specific to chip design -- specifically for 2.5/3D ics -- and this issue is getting a lot of attention.

Heavy use of decoupling capacitors can affect layout planning, layout, and design choices at all three levels, with associated negative effects on costs. However, the current change caused by inductance parasitism will depend on the current consumption at the chip level, and can draw more current from the on-chip regulator - a very undesirable event, as the on-chip regulator is the source of the parasitic capacitance. The decoupling cap plays a crucial role here because it is a "rechargeable battery" that balances the current. Therefore, the use of decoupling caps is an unavoidable reality.

We can clearly see from the above information that there is an increasing interdependence between successful chip, package and PCB design.

From chip to package to PCB

Chip vendors discovered some time ago that building demo boards for chips is much easier than developing full-fledged system implementations. However, in the SoC era, semiconductor vendors are beginning to realize that their field is rapidly converging with packaging and PCB circuit board. As we can now see very clearly, this convergence is driven by the need to integrate digital and analog IP of extraordinary complexity and functionality into silicon wafers. In other words: In order to properly integrate system IP into silicon chips, chip developers must actually become system developers.

This has become a requirement for chip design teams to expand their skills in order to co-develop at the chip, package, and board levels throughout the full modeling, design, simulation, and verification cycle. EDA vendors are trying to respond to this emerging demand by offering new tools and processes to incorporate into the chip-development tool chain.

A comprehensive approach to chip, package and PCB co-design

An important addition is the incorporation of each level of prototyping in successive layers of abstraction, from high abstractions - black box modeling - to medium abstractions - trial layouts and more complete rough layout and wiring of chip blocks combined with physics. Prototype the package and PCB, and finally reach a low or zero abstraction level when the logic design is complete. Here, SoC design curing, physical design and integration issues dominate. By dynamically participating in the co-design between all three levels from the beginning, IP integration issues can be resolved through planning and optimization cycles prior to the final flow piece, and difficulties such as schedule delays and iterative rework can be avoided.

Regardless of the effectiveness of any given EDA tool or process, it is clear at this point that designing the chip and integrating its digital and analog IP, then optimizing the placement of the chip in the package chosen and in turn optimizing the placement of the device on a PCB that is no longer sufficiently multilayered, has successive phases of continuous completion and relative isolation. Independent participation at each level will ensure significant cost overruns, schedule delays, and wasted work cycles on redesign.

The integration of semiconductor digital and analog IP is timely, efficient, and fully successful only when the chip design team takes into account the "vertical" dimension of SoC and addresses all three including detailed package and PCB board parameters in the design, simulation, and verification process. The level is a system. SoC development is no longer just a silicon-based discipline. To properly represent the functional richness of SoCs filled with digital, analog, RF, and mixed-signal IP modules, from now on, chip design teams will be required to encroach further into the engineering domain of system manufacturers, beyond the logical level and into physics as well.