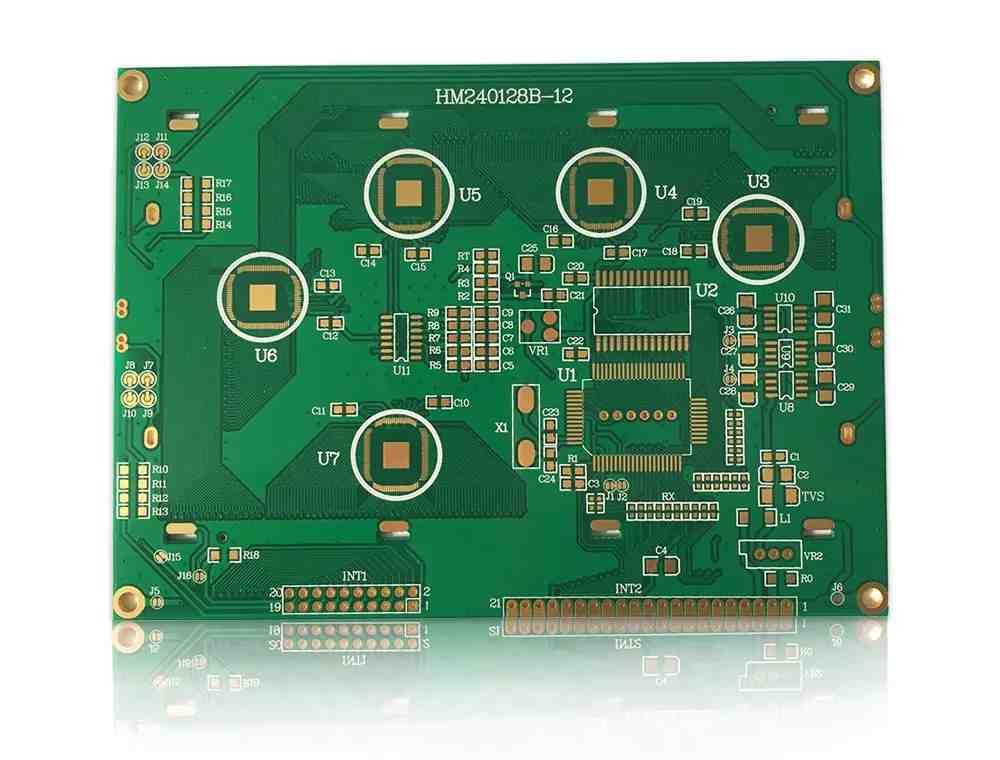

Experience summary of circuit board factory explaining the layout of DDR2 PCB

PCB Assembly and PCB processing manufacturers explain DDR2 PCB layout experience summary, signal grouping, data group and stack structure

Signal grouping:

DDR2 BUS signals are usually wired into several groups, and the signals of the same group have related or similar signal characteristics.

Clock group: differential clock signal, each pair of signals are of the same frequency and phase. Ck0p and ck0n are a pair.

Data groups: For the 64 bit DDR2 motherboard memory, every 8 bits (that is, a byte) of data can be divided into eight groups, including data dq [0:7], data mask dqm0, data gating differential signal dqsp0 and dqsn0, and so on. The signals of the same data group should be routed on the same layer, and the layers should also be changed together. The number of VIAs should be the same. The data bits can be interchanged for the convenience of routing in the same signal layer. For example, when routing the dq2 signal, it is found that if the wiring is routed according to the schematic diagram, it will be staggered with the dq4 signal. In this way, we have to change layers to route the signal. We can make the signal go to the same layer by exchanging data bits. For memory, what is stored in each bit is what is read. The exchange will not be affected, but the exchange condition must be between eight bits in the same group.

Address/command group: MA [0:14], BA0, BA1, BA2, RAS, CAS, WE

Control group: the clock enable CKE, chip select CS, and terminal resistor gate ODT are a group. For memory modules, DIMM0 uses CKE0, CKE1, CS0, CS1, ODT0, and ODT1. When designing on-board memory, only CKE0, CS0 and ODT0 can be used to control four 16 bit memory chips.

PCB stack up:

For a six ply board, the general laminations are top, GND, singnal2, singnal3, POWER, and bottom. Generally, it is better to take GND as the reference plane for signals. The impedance of the routing is determined by the routing width, the copper foil thickness of the routing, the distance from the routing to the reference plane, the copper foil thickness of the reference plane, and the plate dielectric material. When designing a PCB, the stack should be set according to the impedance design requirements of the CPU manufacturer. General PCB design software can also calculate the impedance. Find the PCB manufacturer to know the information about the thickness of the plate medium, and then you can design the stack and line width by yourself. The address/command signal and control signal can take the 1.8V memory working voltage as the reference plane. However, a complete power plane must be referenced.

Routing length control:

For high-frequency signals like DDR2, the routing length should be calculated to the CPU core, which introduces a concept called package length. Silicon wafer is etched into CPU core by physical and chemical methods, and then it is our common CPU to package the CPU core onto a small PCB substrate. The routing length from the pin on the small PCB to the CPU core is called the package length, also called PIN delay.

The clock length to the same rank memory should be controlled within plus or minus 5mil.

The length of all wires in the same data group should be controlled within plus or minus 20 mils of the data strobe signal DQS. The length can be different between different data groups, but should be controlled within plus or minus 500 mils of the clock signal.

The length of the address/command group signal is not strictly controlled, and the INTEL Atomizing N450 is required to be controlled within the range of negative 500mil to positive 1000mil of the clock signal. That is to say, the difference between the longest signal and the shortest signal can be 1500mil, but it is better to reduce the difference in signal length when wiring. When wiring, it is no problem that the length of this group of signals is completely equal, but it also takes a lot of PCB space and time. If the address/command signal length exceeds the clock signal by thousands of mils, it needs to be properly adjusted in the BIOS firmware. It should be controlled within the range required by the CPU. When it is necessary to do on-board memory, you only need to configure the memory SPD.

The control requirements for the signal length of the control group are similar to those for the address/command group signal. The design should be carried out according to the requirements of the CPU manufacturer. The INTEL Agitation N450 is required to be controlled within the clock signal of 0 mil to+1000 0mil.

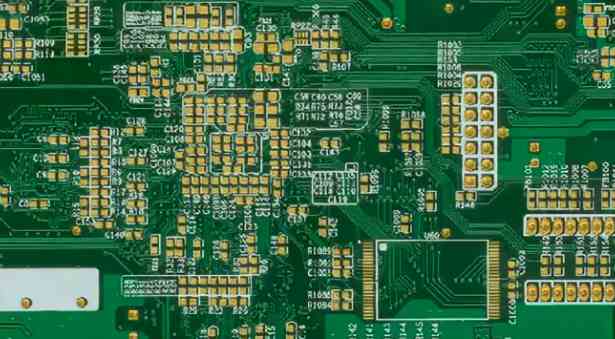

Wire spacing:

Generally speaking, the routing should follow the 3W principle, that is, the distance between the same horizontal line and the line is 3 times the width of the line. However, this is not necessary. The requirements of Intel are relatively small. In general, the spacing between winding lines can be 16 to 20 mil, and the clock signal can be increased to 30 mil. The distance between different groups of signals should be appropriately extended, which can be more than 20mil, and the distance between address/command group and control group signals can be smaller than 8mil. The distance between BGA fan outs can be small, and the outgoing line should be routed according to the CPU design requirements.

Other POWER routing:

VREF wiring can use a 20mil wire, and a 0.1uf capacitor should be added to each device connected.

VTT wiring should be more than 135mil. Every four resistors should be connected with a 0.1uf capacitor, and both ends should be connected with a 10uf large capacitor.

Point to multipoint signals, such as address/command signals, control signals, and clock signals, should be routed in a "T" shape, that is, the chip should go up and branch in the middle, and the length should meet the CPU design requirements. PCB assembly and PCB processing manufacturers explain DDR2 PCB layout experience summary, signal grouping, data group, and stack structure.