Common problems in FPC circuit design that you should know

1、 Overlap of pads

1. Overlap of bonding pads (except for surface mount pads) means the overlap of holes. During the drilling process, the drill bit will break due to multiple drilling at one place, resulting in hole damage.

2. Two holes in the multilayer board are overlapped. For example, one hole is a spacer plate, and the other hole is a connecting plate (rosette pad). In this way, the negative film is drawn as a spacer plate, resulting in scrapping.

2、 Abuse of graphic layer

1. Some useless connections have been made on some graphic layers, but the original four layer board has designed more than five layers of circuits, causing misunderstanding.

2. The design time diagram is convenient. Take Protel software as an example, use the Board layer to draw lines that all layers have, and use the Board layer to draw marking lines. In this way, when photo drawing data, because the Board layer is not selected, the connection is missed and the circuit is broken, or because the marking line of the Board layer is selected, the circuit is short circuited. Therefore, the integrity and clarity of the graphic layer are maintained during the design.

3. It violates the conventional design, for example, the component surface is designed at the bottom layer, and the welding surface is designed at the top, causing inconvenience.

3、 Random placement of characters

1. The SMD pad of the character cover pad brings inconvenience to the on-off test of the printed board and the welding of components.

2. The design of characters is too small, which makes it difficult to screen print, and too large makes characters overlap and difficult to distinguish.

4、 Hole diameter setting of single-sided pad

Single side pads generally do not drill holes. If the holes need to be marked, the hole diameter should be designed as zero. If the numerical value is designed, the hole coordinates will appear at this position when the drilling data is generated, causing problems.

2. Single side pads such as drilling holes shall be specially marked.

5、 Draw pads with filler blocks

The pad drawn with filler block can pass DRC inspection when designing the circuit, but it cannot be processed. Therefore, such pads cannot directly generate solder resistance data. When the solder resistance is applied, the filler block area will be covered by the solder resistance, resulting in difficulty in device welding.

6、 The electrical layer is both a mosaic pad and a connection

Because the power supply designed as a rosette pad is contrary to the image on the actual printed board, and all connections are isolation lines, the designer should be very clear about this. By the way, be careful when drawing several groups of power supply or several kinds of ground isolation lines. Do not leave gaps to short circuit two groups of power supply, or block the connected area (separate one group of power supply).

7、 Unclear definition of processing level

1. The single panel is designed on the TOP layer. If no instructions are given, it may be difficult to weld the fabricated board with components.

2. For example, when designing a four layer board, the TOP mid1 and mid2 bottom layers are used, but they are not placed in this order during processing, which requires explanation.

8、 Too many filler blocks in the design or the filler blocks are filled with very thin lines

1. The photo data is lost and incomplete.

2. Because fill blocks are drawn one by one in photo data processing, the amount of photo data generated is quite large, which increases the difficulty of data processing.

9、 surface mount device pad too short

This is for on-off test. For a surface mount device that is too dense, the distance between its two pins is quite small, and the bonding pad is also quite thin. When installing the test pin, it must be staggered up and down (left and right). If the bonding pad is designed to be too short, it will not affect the device installation, but it will make the test pin stagger.

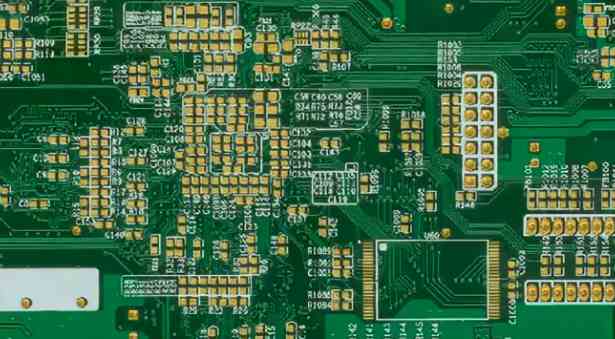

10、 Spacing between large grids is too small

The edge between the large area grid lines and the same line is too small (less than 0.3mm). During the PCB manufacturing process, the drawing transfer process is prone to produce a lot of broken films attached to the board after the development, resulting in wire breakage.

11、 Large area copper foil is too close to the outer frame

The distance between the large area copper foil and the outer frame shall be at least 0.2mm, because it is easy to cause the copper foil to rise and the solder resist to fall off when milling the shape.

12、 Unclear outline frame design

Some customers have designed contour lines in Keep layer, Board layer, Top over layer, etc., and these contour lines do not coincide, which makes it difficult for PCB manufacturers to determine which contour line should prevail.

13、 Uneven graphic design

In the process of pattern electroplating, the coating is uneven, which affects the quality.

XIV. Grid lines shall be applied when the copper area is too large to avoid foaming during SMT

PCB manufacturers, PCB designers and PCBA manufacturers will explain common problems in FPC circuit design.