PCB Design Process Considerations

Gigabit serial I/O technology has extremely excellent performance, but these superior performance needs conditions to ensure, that is, excellent signal integrity For example, a bit vendor reported that when they first tried to use a high-speed, application specific gigabit serial design, the failure rate was 90 percent In order to improve the success rate, we may need to make an analogy and adopt a more complex new bypass circuit

The GTP performance of Spartan-6 FPGA depends on the printed circuit board. The following factors need to be considered in the test: PCB design process: board laminate structure, component layout, and signal routing

PCB design

Power supply and stackup

For the GTP transceiver of Spartan-6 FPGA, the stack can be divided into two groups, the distribution layer and the signal routing layer The power layer is used to connect MGTAVTTTX and MGTAVTTRX power supply pins of MGTACC, MGTAVCCPLL, GTP

In the stack, the horizontal transmission signal line provides the signal return path At the same time, because there is a mask between the two signal layers, when routing signals, it is unnecessary to consider the problems of adjacent layer routing and provide more signal paths

The power plane of GTP shall be closely adjacent to the ground plane to increase coupling effect The ground plate can provide a mask for the power supply surface of GTP and shield the power plane from noise interference caused by upper or lower signals

In fact, from another point of view, when power supply noise occurs in the high frequency range, with the increase of frequency, it is increasingly difficult to find a capacitor that can cover the frequency range and achieve filtering effect until it is impossible to find such a capacitor With the decrease of capacitance, the stray inductance and resistance of the package will not change correspondingly, and the frequency response will not change much In order to achieve better power distribution at high speeds, we need to use power layers and ground planes to build our own capacitors In order to achieve our goal more effectively, it is usually necessary to use adjacent power planes and ground planes

The connection between GTP power supply pin and distribution network plays a key role in GTP efficiency PDN, FPGA needs low impedance and low noise connection The GTP power supply of FPGA can withstand the maximum noise of 10mVpp Within the range of 10KHz to 80MHz, small aircraft can be used for power supply This small power board should not cover the area of the SelectIO interface

PCB design

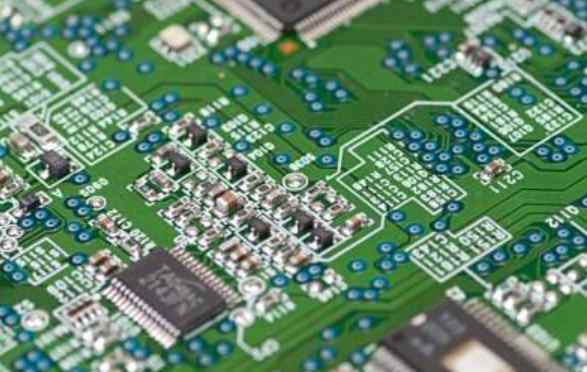

In addition to considering the value of the bypass capacitor, another important aspect to consider is capacitor placement

The general rule is that the larger the capacitance, the less strict the placement requirements If the capacitor value is small, the capacitor should be as close to the power and ground pins as possible One method that can be used is to remove the traces and vias of the unused general-purpose IO to make room for the bypass capacitor

The location of the GTP power segmentation area and the location of the GTP filter capacitor.

Signal routing

GTP signal traces and SelectIO signal traces should be avoided on adjacent layers It is important to keep a certain distance between the difference line pairs and between the difference line and other lines The general rule is that the distance between adjacent line pairs must be at least 5 times the distance between two lines in the line pair

The gigabit signal differential circuit shall avoid changing the wiring layer as much as possible If cross layer transmission is required, you need to be very careful First, you must provide a complete return path Therefore, we must couple the reference layer of layer A with that of layer B The ideal situation is that both reference layers are strata In this case, the return path can be realized by placing another through-hole, which connects the two reference layers near the transport layer If the reference planes are different (one is the ground plane and the other is the power plane), you need to place a 0.01mF capacitor as close to the through-hole as possible to connect two reference planes to reduce the loop impedance There may be many problems in the PCB design process, but as long as every detail is carefully done, a good PCB schematic can be designed