Сборка гибридной печатной платы для малой ячейки RFPD 5G

Функциональность: счетверенные передатчики, счетверенные приемники и двойные приемники наблюдения с 2 входами каждый

Полоса пропускания: приемник 200 MHz,

Передатчик большого сигнала 200 MHz/синтезирующий передатчик 450 MHz

и наблюдательный приемник 450 MHz

Диапазон настройки: от 650 MHz до 6 GHz

Интерфейс: 12 Gbps JESD204B/C 1

Потребляемая мощность: 5 W 2

Синхронизация фазы многочипового гетеродина

Функции DFE: расширенный DPD / CLGC / CFR 3

Пакет: 14 × 14 BGA

1. Будет обновлено до 24,33 Gbps в будущем выпуске

2. Для 25% Rx 75% Tx, 1x Orx вкл., полоса пропускания 200 MHz/450 MHz/450 MHz, затухание 0 dB

3. Поддерживается на ADRV9029, который скоро появится

ADRV9009 vs ADRV9026 – Особенности & арактеристики

Спецификация/Функция | ADRV9008/9 | ADRV9026 |

№ Tx/Rx/Orx | 2T2R1OR | 4T4R2OR |

Поддержка TDD/FDD | Одночиповый TDD Двухчиповый FDD | Одночиповый TDD & FDD |

Диапазон частот | 75MHz – 6GHz | 650MHz – 6GHz1 |

Полоса пропускания канала Rx/Tx/Orx | 200MHz/450MHz/450MHz | 200MHz/450MHz/450MHz |

Потребляемая мощность | 1x | 0.5x |

Максимальная частота дискретизации ADC/DAC | 2Gbps/1Gbps | 5Gbps/2.5Gbps |

Интерфейс | 12Gbps JESD204B | 16Gbps JESD204B & JESD204C |

SERDES переулок | 4 полосы в каждую сторону | 4 полосы в каждую сторону |

Рельсы питания | 1.3V/1.8V/3.3V | 1.0V/1.3V/1.8V |

Упаковка | 12x12 FC-BGA | 12x12 FC-BGA |

Функции DFE | N/A | Встроенный DPD и CFR (с возможностью обхода) для приложений с полосой пропускания до 200 MHz |

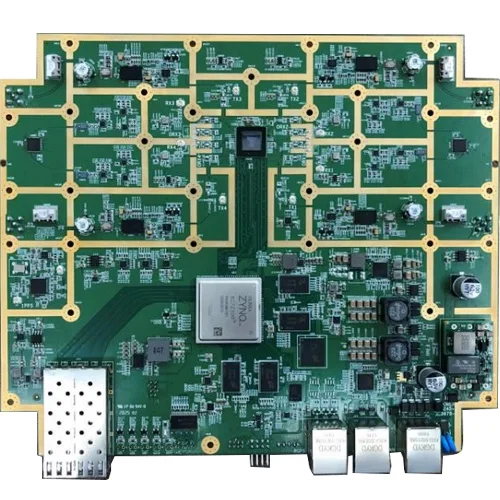

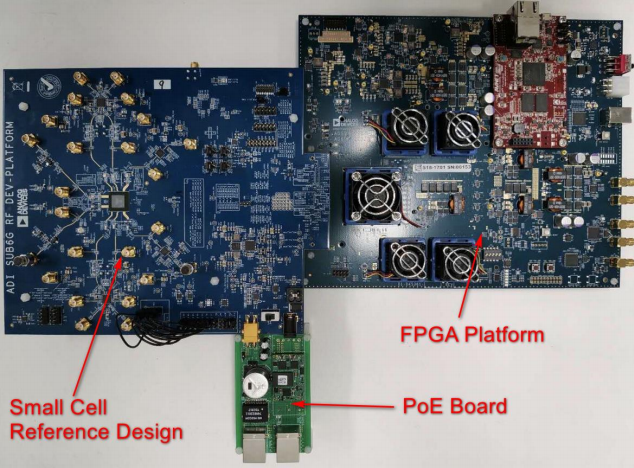

Эталонный проект ADRV9029 для малых сот

► Встроенная эталонная радиочастотная конструкция

▪ Добавьте предварительный каскад PA HMC625B/ADL5611, чтобы эталонная платформа могла напрямую подключаться к PA EVB.

▪ Добавляйте продукты ADI RF Front end ADRF5545A/ADRF5549 на каналы RX и переключайте продукты на каналы ORx.

▪ Обеспечьте одновременную поддержку платой средних и высоких частот.

► Решение для бортовых часов

▪ Используйте устройство синхронизации доменов с двумя часами AD9545.

▪ Добавьте возможность SyncE, необходимую для O-RAN.

► Встроенный источник питания

▪ Используйте ADP5054 в качестве источника питания для ADRV902x и устройств синхронизации.

▪ Оставьте интерфейс для внешнего блока питания PoE EVB + ADI.

► Поддерживается несколько платформ FPGA

▪ Работайте либо с платой ADS9, либо с платой Intel Arria 10.

▪ Общее программное обеспечение с графическим интерфейсом и пользовательский интерфейс

► Поддерживается программное обеспечение для проверки DFE

▪ Интегрировать интерфейс проверки DPD / CFR / CLGC в графический интерфейс.

Kingford предоставляет услуги по сборке Гибридной печатной платы для малой ячейки RFPD 5G. Это универсальный завод по сборке печатных плат с большим опытом работы в отрасли. Добро пожаловать на запрос.

Функциональность: счетверенные передатчики, счетверенные приемники и двойные приемники наблюдения с 2 входами каждый

Полоса пропускания: приемник 200 MHz,

Передатчик большого сигнала 200 MHz/синтезирующий передатчик 450 MHz

и наблюдательный приемник 450 MHz

Диапазон настройки: от 650 MHz до 6 GHz

Интерфейс: 12 Gbps JESD204B/C 1

Потребляемая мощность: 5 W 2

Синхронизация фазы многочипового гетеродина

Функции DFE: расширенный DPD / CLGC / CFR 3

Пакет: 14 × 14 BGA

1. Будет обновлено до 24,33 Gbps в будущем выпуске

2. Для 25% Rx 75% Tx, 1x Orx вкл., полоса пропускания 200 MHz/450 MHz/450 MHz, затухание 0 dB

3. Поддерживается на ADRV9029, который скоро появится

- Предыдущий:Сборка печатной платы для датчика XWR6843 mmWave

- Следующий:Нет